## Depletion-mode Ga2O3 metal-oxide-semiconductor field-effect transistors on $\beta$ -Ga2O3 (010) substrates and temperature dependence of their device characteristics

Masataka Higashiwaki, Kohei Sasaki, Takafumi Kamimura, Man Hoi Wong, Daivasigamani Krishnamurthy et al.

Citation: Appl. Phys. Lett. **103**, 123511 (2013); doi: 10.1063/1.4821858 View online: http://dx.doi.org/10.1063/1.4821858 View Table of Contents: http://apl.aip.org/resource/1/APPLAB/v103/i12 Published by the AIP Publishing LLC.

## Additional information on Appl. Phys. Lett.

Journal Homepage: http://apl.aip.org/ Journal Information: http://apl.aip.org/about/about\_the\_journal Top downloads: http://apl.aip.org/features/most\_downloaded Information for Authors: http://apl.aip.org/authors

## Depletion-mode $Ga_2O_3$ metal-oxide-semiconductor field-effect transistors on $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) substrates and temperature dependence of their device characteristics

Masataka Higashiwaki,<sup>1,a)</sup> Kohei Sasaki,<sup>1,2</sup> Takafumi Kamimura,<sup>1</sup> Man Hoi Wong,<sup>1</sup> Daivasigamani Krishnamurthy,<sup>1</sup> Akito Kuramata,<sup>2</sup> Takekazu Masui,<sup>3</sup> and Shigenobu Yamakoshi<sup>2</sup> <sup>1</sup>National Institute of Information and Communications Technology, 4–2–1 Nukui-Kitamachi, Koganei, Tokyo 184–8795, Japan <sup>2</sup>Tamura Corporation, 2–3–1 Hirosedai, Sayama, Saitama 350–1328, Japan <sup>3</sup>Koha Co., Ltd., 2–6–8 Kouyama, Nerima, Tokyo 176–0022, Japan

(Received 31 July 2013; accepted 5 September 2013; published online 20 September 2013)

Single-crystal gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) metal-oxide-semiconductor field-effect transistors were fabricated on a semi-insulating  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) substrate. A Sn-doped *n*-Ga<sub>2</sub>O<sub>3</sub> channel layer was grown by molecular-beam epitaxy. Si-ion implantation doping was performed to source and drain electrode regions for obtaining low-resistance ohmic contacts. An Al<sub>2</sub>O<sub>3</sub> gate dielectric film formed by atomic layer deposition passivated the device surface and significantly reduced gate leakage. The device with a gate length of 2  $\mu$ m showed effective gate modulation of the drain current with an extremely low off-state drain leakage of less than a few pA/mm, leading to a high drain current on/off ratio of over ten orders of magnitude. A three-terminal off-state breakdown voltage of 370 V was achieved. Stable transistor operation was sustained at temperatures up to 250 °C. © 2013 AIP Publishing LLC. [http://dx.doi.org/10.1063/1.4821858]

We have been proposing gallium oxide  $(Ga_2O_3)$  as a promising candidate for power device applications because of its excellent material properties and suitability for mass production.<sup>1,2</sup> With a wide bandgap of  $4.7-4.9 \,\mathrm{eV}$ ,<sup>3-5</sup> the estimated breakdown electric field of 8 MV/cm for Ga<sub>2</sub>O<sub>3</sub> is about three times larger than those of SiC and GaN. Ga<sub>2</sub>O<sub>3</sub> can be controllably doped to obtain electron densities (*n*) from semi-insulating to as high as  $10^{19} \text{ cm}^{-3}$ . The extrapolated experimental bulk electron mobility of  $Ga_2O_3$  reaches a relatively high value of about  $300 \text{ cm}^2/\text{V}\cdot\text{s}$ for  $n = 10^{15} - 10^{16} \text{ cm}^{-3}$ , which is typical for the drift layers of vertical power transistors and diodes.<sup>10</sup> This is supported by theoretical calculations showing that the electron effective mass of  $0.23-0.34m_0$  ( $m_0$ : free electron mass) for  $Ga_2O_3$  is comparable to those for conventional widegap (3–4 eV) semiconductors.<sup>5,8,11</sup> The Baliga's power device figure of merit of Ga<sub>2</sub>O<sub>3</sub> is estimated to be several times larger than those of SiC and GaN based on their material properties,<sup>1</sup> projecting higher breakdown voltages  $(V_{\rm br})$  and efficiencies for Ga<sub>2</sub>O<sub>3</sub> power devices than their SiC and GaN counterparts. The other important attribute of Ga<sub>2</sub>O<sub>3</sub> is that single-crystal bulk materials can be synthesized by using conventional melt growth techniques such as the floating-zone (FZ), the edge-defined film-fed growth, and Czochralski methods.<sup>12–15</sup> These technologies, which are currently employed for manufacturing sapphire substrates, will offer Ga<sub>2</sub>O<sub>3</sub> a big advantage over other widegap semiconductors by enabling simple and low-cost mass production of single-crystal native Ga<sub>2</sub>O<sub>3</sub> substrates. Therefore,  $Ga_2O_3$  power devices have the obvious potential to surpass

SiC and GaN in not only device performance but also cost effectiveness.

We have previously demonstrated Ga<sub>2</sub>O<sub>3</sub> metalsemiconductor field-effect transistors (MESFETs) on singlecrystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> substrates.<sup>1</sup> The MESFET showed excellent device characteristics such as a three-terminal off-state  $V_{\rm br}$ of 250 V and a drain current  $(I_d)$  on/off ratio of about four orders of magnitude. However, the device suffered from high contact resistance of source and drain electrodes. In addition, its  $I_d$  on/off ratio was limited by a small leakage current through the unpassivated Ga2O3 surface. To address these shortcomings, we fabricated Ga<sub>2</sub>O<sub>3</sub> metal-oxide-semiconductor FETs (MOSFETs) in the present work by adopting Si-ion (Si<sup>+</sup>) implantation doping for improved ohmic contacts and atomic layer deposition (ALD) of a dielectric film for surface passivation and gate insulation. Temperature dependences of current-voltage (I-V) characteristics of the Ga<sub>2</sub>O<sub>3</sub> MOSFETs were closely examined to estimate their capability for high-temperature application.

The depletion-mode Ga<sub>2</sub>O<sub>3</sub> MOSFETs were fabricated on Fe-doped semi-insulating single-crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) FZ substrates. A 300-nm-thick *n*-Ga<sub>2</sub>O<sub>3</sub> channel layer with a nominal Sn doping concentration of  $7 \times 10^{17}$  cm<sup>-3</sup> was grown by molecular-beam epitaxy at a substrate temperature of 560 °C and a growth rate of 0.6  $\mu$ m/h. Ga and Sn fluxes were, respectively, supplied by Ga metal and SnO<sub>2</sub> powder from conventional Knudsen cells. A gas mixture of ozone and oxygen was used as the oxygen source. The activation energy of Sn in Ga<sub>2</sub>O<sub>3</sub> was estimated to be about 60 meV from the temperature dependence of *n*; therefore, a little less than half of the Sn dopants were activated in the Ga<sub>2</sub>O<sub>3</sub> epitaxial layer at room temperature (RT). In fact, an effective carrier density (*N*<sub>d</sub>-*N*<sub>a</sub>) of about  $3 \times 10^{17}$  cm<sup>-3</sup> was

0003-6951/2013/103(12)/123511/4/\$30.00

<sup>&</sup>lt;sup>a)</sup>Electronic mail: mhigashi@nict.go.jp

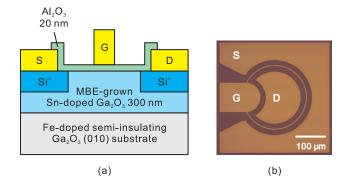

FIG. 1. (a) Schematic cross-section and (b) optical micrograph of depletion-mode  $Ga_2O_3$  MOSFET.

experimentally confirmed for the channel layer at RT by capacitance–voltage measurements on MOS diodes simultaneously fabricated on the same substrate.

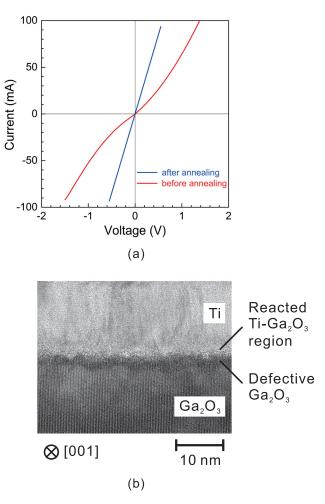

Figures 1(a) and 1(b) show a cross-sectional schematic and an optical micrograph of the Ga<sub>2</sub>O<sub>3</sub> MOSFET, respectively. We employed a circular FET pattern as shown in Fig. 1(b). Multiple Si<sup>+</sup> implantations were performed to the regions for source and drain electrodes to form a 150nm-deep box profile with  $Si = 5 \times 10^{19} \text{ cm}^{-3}$ , followed by 30-min activation annealing at 925 °C in a N2 gas atmosphere by using an infrared-lamp annealing system. The nearsurface region of the implanted areas had a lower Si density due to the nature of the ion implantation process. To expose the highly doped subsurface layer for direct contact with the ohmic metal, a 13-nm-deep recess was performed to the implanted regions by BCl<sub>3</sub> reactive ion etching (RIE) at chamber pressure of 5.0 Pa and plasma power of 100 W prior to evaporation of Ti(20 nm)/Au(230 nm) and liftoff. To further reduce the contact resistance, the Ti/Au metal stack was annealed at 470 °C for 1 min in N<sub>2</sub> by using a rapid thermal annealing system. As shown in Fig. 2(a), the annealed Ti/Au contacts on an implanted Ga<sub>2</sub>O<sub>3</sub> film with Si =  $5 \times 10^{19}$  cm<sup>-3</sup> were ohmic with linear I-V behavior whereas the nonannealed ones showed weak Schottky behavior. The specific contact resistance of the annealed electrodes as measured by the circular transmission-line method was as low as  $8.1 \times 10^{-6} \,\Omega \cdot \mathrm{cm}^2$ , which is comparable to typical values for conventional Ti/Al-based alloyed contacts on n-GaN and/or AlGaN/GaN heterostructures. Cross-sectional transmission electron microscopy (TEM) revealed a defective Ga2O3 region and a reacted Ti-Ga2O3 region at the annealed  $Ti/Ga_2O_3$  interface [Fig. 2(b)]. We speculate that these interfacial reactions contributed to the improved contact ohmicity. Further details of the Si<sup>+</sup> implantation doping in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> and its application to fabrication of low-resistance ohmic contacts have been reported elsewhere.<sup>16</sup> Next, a 20-nm-thick Al<sub>2</sub>O<sub>3</sub> gate dielectric and passivation film was formed on the Ga<sub>2</sub>O<sub>3</sub> layer by plasma-assisted ALD at 250 °C using trimethylaluminum and oxygen plasma. The inductively coupled plasma (ICP) power was 300 W, the O<sub>2</sub> gas flow rate was 20 sccm, and the Al<sub>2</sub>O<sub>3</sub> deposition rate was 0.9 Å/cycle. The gate metal was formed with Ti(3 nm)/Pt(12 nm)/Au(280 nm)on top of the Al<sub>2</sub>O<sub>3</sub> film. Probing pads of the source and drain electrodes were subsequently opened by BCl<sub>3</sub> ICP-RIE. We fabricated and characterized two types of devices with a gate

FIG. 2. (a) I-V characteristics of implanted  $Ga_2O_3$  film before and after Ti/Au electrode annealing. The electrode separation was 24  $\mu$ m. (b) Cross-sectional TEM micrograph of the Ti/Ga<sub>2</sub>O<sub>3</sub> interface after annealing at 470 °C.

length ( $L_g$ ) of 2 or 4  $\mu$ m. The gate width, source-drain implant spacing, and diameter of the inner circular drain electrode were 500, 20, and 200  $\mu$ m, respectively.

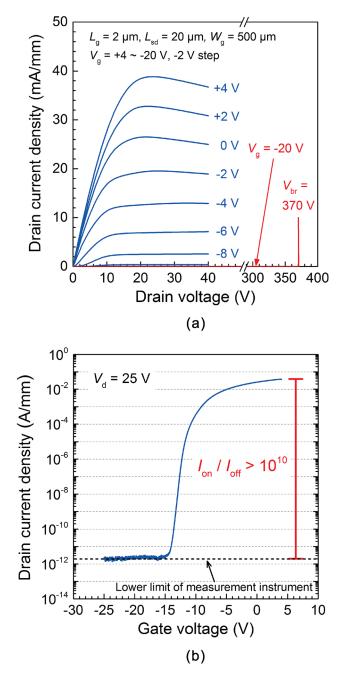

Figure 3(a) shows the DC I-V curves of the  $Ga_2O_3$ MOSFET with  $L_g = 2 \ \mu m$  measured at RT. The  $I_d$  was effectively modulated by the gate voltage  $(V_g)$  with good saturation and sharp pinch-off characteristics. The maximum  $I_d$ was 39 mA/mm for  $V_g = +4$  V. Device self-heating caused by the poor thermal conductivity of the Ga<sub>2</sub>O<sub>3</sub> substrate gave rise to the negative output conductance with increasing drain voltage  $(V_d)$ . The three-terminal off-state  $V_{br}$ , limited by catastrophic dielectric breakdown at the drain side of the gate, was as large as 370 V at  $V_{\rm g} = -20$  V. Figure 3(b) shows the RT transfer characteristics of the MOSFET for  $V_d = 25$  V. The  $I_{\rm d}$  on/off ratio was extremely high, exceeding ten orders of magnitude with the measured off-state leakage of a few pA/mm reaching the lower limit of the measurement instrument. These Ga<sub>2</sub>O<sub>3</sub> MOSFET characteristics were superior to those of the  $Ga_2O_3$  MESFETs we had reported previously, which we attribute to not only the large decrease in the contact resistance with Si<sup>+</sup>-implanted source and drain electrodes but also the low leakage current owing to the Al<sub>2</sub>O<sub>3</sub> gate dielectric.

FIG. 3. (a) DC *I-V* curves and (b) transfer characteristics at  $V_d = 25$  V of Ga<sub>2</sub>O<sub>3</sub> MOSFET ( $L_g = 2 \mu m$ ) measured at RT.

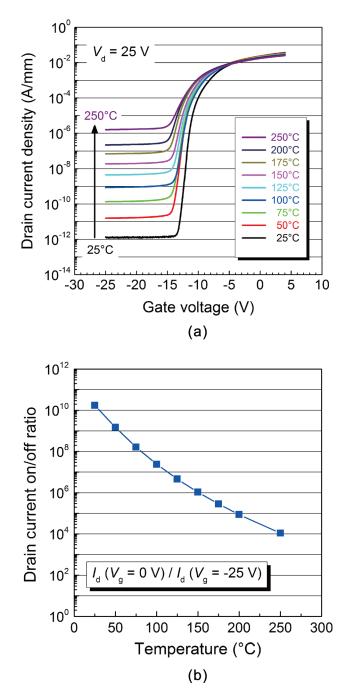

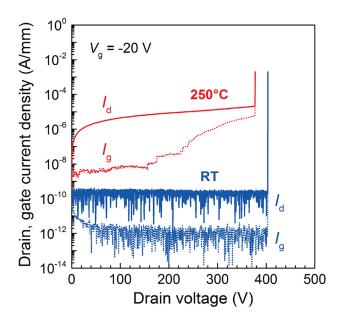

Next, we investigated the performance of the Ga<sub>2</sub>O<sub>3</sub> MOSFET at elevated temperatures. The temperaturedependent measurements were performed in atmosphere by using an on-chip probing setup equipped with a heated sample stage. Figure 4(a) illustrates the temperature-dependent transfer characteristics of the MOSFET with  $L_g = 2 \mu m$  at  $V_d = 25$  V. The corresponding  $I_d$  on/off ratios, defined as the  $I_d$  at  $V_g = 0$  V divided by the  $I_d$  at  $V_g = -25$  V, are plotted in Fig. 4(b). These device characteristics evolved smoothly with increasing device operating temperature. No kinks or abrupt changes that might be indicative of breakdown events and/or permanent degradation were observed, suggesting stable device operation in the whole temperature range from 25 to 250 °C, despite a modest reduction in the maximum  $I_d$  of approximately 30%. The MOSFET maintained a high  $I_d$  on/off ratio of approximately  $10^4$  even at  $250 \,^{\circ}$ C as shown in Fig. 4(b). Furthermore, after high-temperature operation at 250  $^{\circ}$ C and cooling down to RT, the MOSFET exhibited fully recovered device characteristics. Figure 5 plots drain and gate currents ( $I_d$  and  $I_g$ ) under the pinch-off condition of Ga<sub>2</sub>O<sub>3</sub> MOSFETs with  $L_g = 4 \,\mu$ m measured at RT and 250  $^{\circ}$ C. Different-type source-measure units, which had lower detection limits of about 200 and 2 pA/mm, were used for the measurements of  $I_d$  and  $I_g$ , respectively. In case of the RT operation, both the off-state  $I_d$  and  $I_g$  remained below the respective detection limits within the applied  $V_d$  range up to the device breakdown. Even at 250  $^{\circ}$ C, the  $I_d$  and  $I_g$  still kept small values of less than about 20 and 378 V for RT and 250  $^{\circ}$ C,

FIG. 4. (a) Transfer characteristics at  $V_d = 25$  V and (b)  $I_d$  on/off ratios of Ga<sub>2</sub>O<sub>3</sub> MOSFET ( $L_g = 2 \mu m$ ) as a function of operating temperature.

FIG. 5. Off-state breakdown characteristics of Ga<sub>2</sub>O<sub>3</sub> MOSFETs ( $L_g = 4 \mu m$ ) operating at RT and 250 °C;  $V_g = -20$  V.

respectively. The device breakdowns occurred at both temperatures were permanent ones caused by destructive degradation of the Al<sub>2</sub>O<sub>3</sub> dielectrics and gate electrodes. This is consistent with the  $I_d$  and  $I_g$  behaviors that increased significantly at the point of  $V_{br}$  due to a short-circuiting between the gate and drain electrodes. All these results indicate that the Ga<sub>2</sub>O<sub>3</sub> MOSFET can perform at elevated temperatures up to at least 250 °C without noticeable irreversible degradation in electrical characteristics.

In summary, we succeeded in demonstrating depletionmode Ga<sub>2</sub>O<sub>3</sub> MOSFETs on single-crystal  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> (010) substrates. Despite a simple device structure, the MOSFETs with  $L_g = 2 \ \mu m$  demonstrated excellent device characteristics represented by a maximum  $I_d$  of 39 mA/mm for  $V_g = +4$  V, an  $I_d$  on/off ratio of over ten orders of magnitude, and a three-terminal  $V_{\rm br}$  of 370 V. The devices also showed good performance at 250 °C with no significant permanent degradation. These results demonstrate the great potential of Ga<sub>2</sub>O<sub>3</sub> electron devices for power electronics applications in the near future.

This work was partially supported by "The research and development project for innovation technique of energy conservation" of the New Energy and Industrial Technology Development Organization (NEDO).

- <sup>1</sup>M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Lett. **100**, 013504 (2012).

- <sup>2</sup>K. Sasaki, M. Higashiwaki, A. Kuramata, T. Masui, and S. Yamakoshi, IEEE Electron Device Lett. **34**, 493 (2013).

- <sup>3</sup>H. H. Tippins, Phys. Rev. **140**, A316 (1965).

- <sup>4</sup>M. Orita, H. Ohta, M. Hirano, and H. Hosono, Appl. Phys. Lett. **77**, 4166 (2000).

- <sup>5</sup>H. He, R. Orlando, M. A. Blanco, R. Pandey, E. Amzallag, I. Baraille, and M. Rérat, Phys. Rev. B **74**, 195123 (2006).

- <sup>6</sup>N. Ueda, H. Hosono, R. Waseda, and H. Kawazoe, Appl. Phys. Lett. **70**, 3561 (1997).

- <sup>7</sup>E. G. Víllora, K. Shimamura, Y. Yoshikawa, T. Ujiie, and K. Aoki, Appl. Phys. Lett. **92**, 202120 (2008).

- <sup>8</sup>J. B. Varley, J. R. Weber, A. Janotti, and C. G. Van de Walle, Appl. Phys. Lett. **97**, 142106 (2010).

- <sup>9</sup>K. Irmscher, Z. Galazka, M. Pietsch, R. Uecker, and R. Fornari, J. Appl. Phys. **110**, 063720 (2011).

- <sup>10</sup>K. Sasaki, A. Kuramata, T. Masui, E. G. Víllora, K. Shimamura, and S. Yamakoshi, Appl. Phys. Express 5, 035502 (2012).

- <sup>11</sup>K. Yamaguchi, Solid State Commun. **131**, 739 (2004).

- <sup>12</sup>E. G. Víllora, K. Shimamura, Y. Yoshikawa, K. Aoki, and N. Ichinose, J. Cryst. Growth **270**, 420 (2004).

- <sup>13</sup>H. Aida, K. Nishiguchi, H. Takeda, N. Aota, K. Sunakawa, and Y. Yaguchi, Jpn. J. Appl. Phys., Part 1 47, 8506 (2008).

- <sup>14</sup>Y. Tomm, P. Reiche, D. Klimm, and T. Fukuda, J. Cryst. Growth **220**, 510 (2000).

- <sup>15</sup>Z. Galazka, R. Uecker, K. Irmscher, M. Albrecht, D. Klimm, M. Pietsch, M. Brützam, R. Bertram, S. Ganschow, and R. Fornari, Cryst. Res. Technol. 45, 1229 (2010).

- <sup>16</sup>K. Sasaki, M. Higashiwaki, A. Kuramata, T. Masui, and S. Yamakoshi, Appl. Phys. Express 6, 086502 (2013).